# DIGITAL SOUND DETECTOR

# BY

# YINUSA MUSBAU DEJI 98/7296EE

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING SCHOOL OF ENGINEERING AND ENGINEERING TECHNOLOGY FEDERAL UNIVERSITY OFTECHNOLOGY MINNA, NIGER STATE NIGERIA

THIS PROJECT IS SUBMITTED TO THE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING IN PARTIAL FULFILMENT OF THE REQUIREMENT FOR THE AWARD OF A DEGREE OF BACHELOR OF ENGINEERING (B. ENG)

**NOVEMBER 2004**

# **DIGITAL SOUND DETECTOR**

BY

# YINUSA MUSBAU DEJI 98 / 7296EE

A PROJECT SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENT FOR THE AWARD OF BACHELOR OF ENGINEERING (B. ENG.) DEGREE IN THE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING, SCHOOL OF ENGINEERING AND ENGINEERING TECHNOLOGY, FEDERAL UNIVERSITY OF TECHNOLOGY, MINNA, NIGER STATE.

## **DECLARATION**

I, YINUSA MUSBAU DEJI hereby declare that the idea and execution of this project was carried by me, under the supervision of Mr. Abraham Usman Department Electrical and Computer Engineering, Federal University of Technology, Minna.

-----

SIGNATURE OF STUDENT

DATE

## **CERTIFICATION**

This is to certify that this work titled Digital Sound Detector under the supervision of Mr. Abraham Usman for the Award of Bachelor of Engineering in Electrical and Computer Engineering (B. Eng) Department, Federal University of Technology, Minna.

| 09/12/04  |

|-----------|

| DATE      |

|           |

| 9/12/2004 |

| DATE      |

|           |

|           |

(EXTERNAL EXAMINER)

DATE

## DEDICATION

This project is dedicated to Sheik Muhammed Jamiu Bulala and Alhaji Aliu Adebayo Olokoba (RTA).

#### **ACKNOWLEDGEMENTS**

I Wish to express my sincere thanks to Engr. Abraham Usman for his supervision of this project an constructive criticism of the thesis write-up.

My sincere appreciation goes to my parents, Alhaji and Hajia H.A Adebowale Yunus for their financial support, love and care.

I also wish to express my profound gratitude to Arc. And Hajia H. Rabiu, Mr. AbdulRazaq Shittu, Lawyer Munir Shittu, Dr. and Mrs. Abdulmojeed Ijaiya, Dr. and Mrs. AbdulHakeem Alabelewe, Engr. Tunde Rabiu Alabelewe & AbdulHakeem Rabiu.

I am greatly indebted to Mr. and Mrs. Folashade Aluko, Mr. Femi Kayode Fatunbi, Mallam Hashim Adebayo and Mr. Tesleem Kayode Adebayo for their consistent encouragement and financial support.

I am particularly grateful to my friends, and colleagues such as Abdulmojeed Raheem, Suleiman Ishola, Lanre Atoyebi, Tunji Olanipekun, Abdulwasiu Lawal, Jimoh Ismail, Sharafa (IRE), Nurudeen Kolawole, Omokanye Kazeem, Abdulwakeel, Habib, Abdul Ganiy, Sheun, Abdulsalam, Kiff Lawal, Motolani, Biola Oladoja, Bilqis El-Rufai and sister Tunrayo Abdulaziz.

I also swish to express my sincere appreciation to Hajia Rashidat Sanni and my lovely sisters Rekia Yetunde Rabiu , Nofsat Omolara Rabiu, Medinat Abiola Adeyemi and Mallam Abdul Ibrahim Baruwa.

Finally, I thank Almighty Allah (S.W.) for his mercy, care, protection, guidance and blessing.

## **ABSTRACT**

The Digital sound Detector is designed to detect sound, sample and covert to Electrical signal by audio amplifier the resultant output signal is fed into 4 bit decade counter and count number of pulses within 1 second and fed the result into seven segment display through latch.

With this, a frequency range of o to 999HZ can be detected and displayed on seven segment display.

## TABLE OF CONTENTS

| TITL | EPAGE                                 | ii   |

|------|---------------------------------------|------|

| DECI | .ARATION                              | iii  |

| CER1 | TIFICATION                            | iv   |

| DED  | CATION                                | v    |

| ACK  | NOWLEDGEMENT                          | - vi |

| ABS  | TRACT                                 | vii  |

| TAB  | LE OF CONTENTS                        | viii |

| CHA  | PTER ONE: GENERAL INTRODUCTION        |      |

| 1.1  | INTRODUCTION                          | - 1  |

| 1.2  | LITERATURE REVIEW                     | 2    |

| 1.3  | AIMS AND OBJECTIVE                    | - 3  |

| 1.4  | PROJECT OUTLINE                       | 4    |

| СНА  | PTER TWO: SYSTEM DESIGN AND ANALYSIS  |      |

| 2.0  | SYSTEM DESIGN AND ANALYSIS            | 5    |

| 2.1  | PRINCIPLE OF OPERATION                | - 5  |

| CHA  | PTER THREE: CONSTRUCTION PROCEDURE    |      |

| 3.1  | CONSTRUCTION PROCEDURE                | - 21 |

| 3.2  | TESTING AND RESULT                    | - 23 |

| CHA  | PTER FOUR: DISCUSSION, CONCLUSION AND |      |

|      | RECOMMENDATION                        |      |

| 4.1  | DISCUSSION OF RESULT                  | 25   |

| 4.2  | CONCLUSION                            | 25   |

| 4.3  | RECOMMENDATION                        | 25   |

|      | REFERENCES                            |      |

|      | CIRCUIT DIAGRAM                       |      |

## CHAPTER ONE

## 1.1 INTRODUCTION

The importance of detection of sound (sound wave) of different frequencies can not be overemphasized in this present age since sound and music are part of our everyday sensory experience. The Digital sound Defector (DSD). Is therefore necessary than ever before.

Digital sound Detector (DSD) is designed to detect sound within a frequency range 0-999 HZ, sample them within specified time (converts to digital signal) and fed the resulted digital into the seven signal to display the frequency of the detected sound.

The principle employed in the demonstration of this project titled Digital sound Defector (DSD) is that when the tunes of a funning fork are hit with rubber mallet, energy will be gained by tuning fork. This gain energy disturbs the particles and forces the object into vibration motion-at its natural frequency. DSD captured the sound and displays the frequence of the tuning fork.

However this project (DSD) cannot be completed without limitation.

These include cost of microphone which why a indirectimal microphone is used.

For better result, special microphone such as gun, ultradirectional could be used.

This project was carried out in order to explore the detection of sound behind music (and noise) soupe and see how the simple soutific and engineering application could be employed.

#### 1.2 LITERATURE REVIEW.

Sound detection and analysis is as for back as human race. The early man in the primitive age could tell whether there was animal closed by hunting. He could easily approximate its direction and distance. Whether a town won or lost a better can be determined from their music (sound). A blind man can tell when it is about to rain. The fact that human being has two ears enable him to detect the direction from which sound in the open reaches him. The normal human ear can only detect the sound within the range of about 20HZ to 20,000 HZ, with some variation from individual to individual.

However, scientists and Engineers for several years have been developing veireus devices for defection of sound for below to defect. It all began with study of sound, which was as far back as ancient times. As early as the 500 BC, Pythagorean, a Greek philosopher and mathematician experiment on sand of vibration string. Another Greek scholar named Archetypal (Enylopaedia Britannica volume 19) many have observed that faster motions result in higher pitch-sound to ears. Hertz, Heinrich Rudolf 1857 (Encyclopaedia Britannica vol 19) was the first to work on frequency of radio wave. All these serious of work and research were carried on sound until 1860 when a German physicist and

psychologist investigated the defection of sound. Through early scientific work in the production and reception of sound in closed space (i.e room of acoustic) was reported around 1850, the modern quantitative foundation of the subject (sound detection) from the work of united state phycist; Wallace clement stabile, who in 1900 found a low to connect the reverberation (echo) time on a closed room with a volume of the room and amount of absorbing material.

However for sand to be stated and applied, sound energy must be defected and transformed to make it perceptible to people or sorsible to cybernetic devices. In any sound defecting instrument, microphone is a transducer for the defection of sound and it was first coined in 1827 and was used to describe a purely acoustic device

In another serse, 1877's publication by the English phycist lord Raleigh (John scarlet) of the theory of sound, in which the whole

## 1.3 AIMS/ OBJECTIVE

The reason behind the designing a Digital sound Defector (DSD) was due to the intrigue behind the manipulation various electrical components, integrated circuit and seven segment display.

Components and formulae encountered in courses such as analogue electronics were used and their principles of operation were better understood. The ability to read values of components and indertification of their polarity were better improved.

The aims and objectives of this project among other include.

- (a) Defection of sound

- (b) Ability to display the frequency of defected sound

## 1.4 PROJECT OUTLINE

Chapter one provides the introduction, literature review, objects

Chapter two is made up of steps involved in the system designs the operating principles of the device were explicitly presented.

Construction, testing, troubleshooting and the result made up chapter three.

Lastly, chapter four contains the conclusion and recommendations white appendix has reference, and circuitry.

### **CHAPTER TWO**

#### 2.0 SYSTEM DESIGN AND ANALYSIS

#### 2.1 PRINCIPLE OF OPERATION

The sound signal is detected by microphone in an immediate environment. Being transducer, it converts a detected sound signal to electrical signal and feed into an audio amplifier. The primary function of an amplifier is to increase the amplitude or power of a signal.

A crystal oscillator generates a frequency of 32, 768HZ, which is fed into frequency/ oscillator divider. The later then first divides the frequency by two in 14 consecutive times to produce different frequencies. Among the resulted frequencies 1 HZ and 2HZ were used. The former is used to enable the decade counter. During. This enabling period, electrical signal from audio amplifier is fed into 4bit decade counter. The 2HZ are to transfer the data into the 4bit latch incoperated into the two 4511B-decade counter. After the counter has been opened, it counts the pulses within one second. The digital output is transferred into seven-segment display to display the frequency of the sound signal or vibrating object via 4-bit latch.

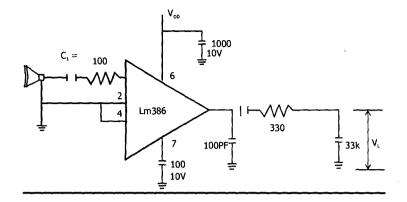

# 2.2 LM 386

$C_1 = \frac{1}{2} TT$  flow R,

Flow = 200 H2 (chosen)

$C1 = 1/_2 \times 1$

$C1 = 7.5 \times 10^6$

C1 = 8 NF

Pin 6

VDD = 5 volts

$V_{C3} > 1.5 \text{ x VDD}$

$V_{C3} > 1.5 \times 5$

$V_{C3} > 7.5V$

Pin 7

VDD = 5 volts

$V_{C3} > 1.5 \text{ x VDD}$

$V_{C3} > 1.5 \times 5$

$V_{C3} > 7.5V$

$C_5 = \frac{1}{2} x^{1/11} x^{1/200} x^{1/RL}$

$$C5 = \frac{1}{400 \times 300 \times TT}$$

$$C5 = 2.65 \times 10^{-6} = 3 \text{ UF}$$

From Voltage Divider theorem and for preservation of signal from LM386, R1 = 330n

$$VL = (\underbrace{33k}_{33k+330n})x \text{ V out}$$

$$VL = 33000$$

x V out  $33330$

$$VL=0.99x V out$$

$VL=1x V out$

:. R1 = 330n

the LM 386 is a power amplifier designed for use in low voltage consumer applications. The gain is internally set to 20 to keep external part constant low, but the addition of an external resistor and capacitor between pin 1 and 8 will increase the gain from any value from 20 to 200.

When configured as shown above, the gain of the amplifier will be 20. This is used in the design of this circuit in order to prevent external noise.

#### 2.3 **CD4060B**

The CD4060 consists of an oscillator section and 14 ripples carry binary counter stages. The oscillator configuration allows design of either Rc or crystal oscillator circuits, the later was used in this design. Reset input is provided which reset. The counter to the all o's state and disables the oscillator. A high

level on the RESET line accomplishes the reset function. All counter stages are master slave flip-flop. The state of the counter is advanced one step in binary order on the negative transition of QI (and Q0). All inputs and out puts are fully buffered. Schinitt trigger action on the input pulse line permits unlimited input pulse rise and fall times.

The CD 4060B features are as written below

- > 12MHZ clock rate at 15V

- > Common reset

- > Fully static operation

- > Buffered inputs and outputs

- > Schmitt trigger input pulse line.

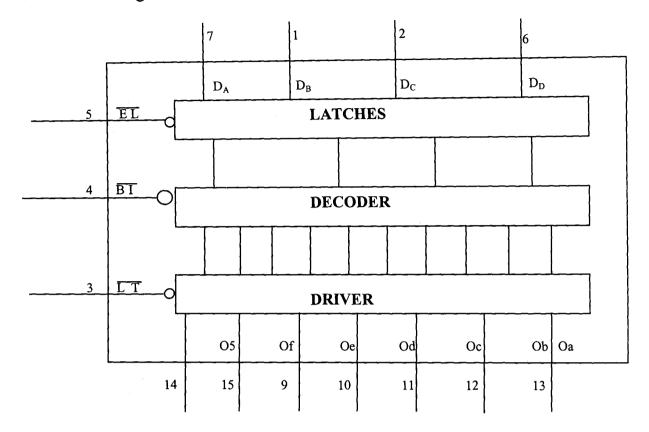

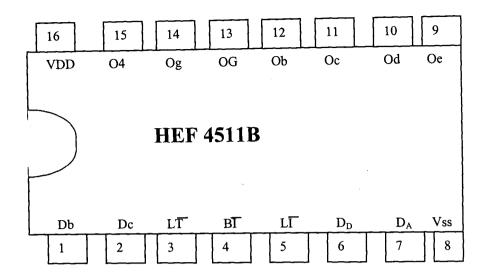

#### 2.4 CD4511B

This is a BCD to 7- segment latch / decoder / drive four address inputs (DA to DD), an active low latch enable input (EL), an active low ripple blank in (BI), an active low lamp test input (LT), and save HIGH n-p-n bipolar transistor segment output (Oa)

Applications of CD4511B include:

- ➤ Driving LED display

- > Driving incandescent displays

- > Driving fluorescent displays

- Driving LCD displays

# > Driving gas discharge displays

The functional diagram of CD4511B is given in

When EL is low, the state of the segment outputs (Og) is determined by the data on DA to DD.

When EL goes High, the last data present on DA to DD stored in the latches and the segment outputs are stable. When LT is low, all the segment output are independent of all other input conditions. With LT low on BT forces all segment output low. The inputs and BT do not affect the latch circuit.

The pinning diagram of CD4511B is given

## **PINNING**

DA to DD address (data) inputs

EL Latch enable input (active low)

BT Ripple blanking input (active low)

Lamp test input (active low)

To Og segment outputs

#### 2.5 CD4029

(iii) The CD4029B is a pre settable up/down computer which counts in either binary or decade mode depending on the voltage level applied at binary / decade input binary / decade is at logical '1', the counter counts binary. Otherwise, it counts in decade. Similarly, counter counts up when the up /down input is at and vice versa

A logical '1' preset enable signal allows in form at the 'jam' input to presets the counter to any asynchronously with the clock. The counter is advances one count at the positive- going edge of the clock carry in and preset enable inputs are at logical Advancement is inhibited when either or both of the inputs is at logical "1". The carry out signal usually at logical "1" state and goes to logical "O" when the counter reaches its maximum count "up" mode of the minimum count in the "down" provided the carry input is at logical "O" state.

All inputs are protected against static chip by diode clamps to both VDD and Vss.

Its features include:

- \* Wide supply voltage range

- High noise immunity

- Low power TTL compatibility

- Parallel jam inputs

Binary or BCD decade up/down counting

### 2.6 SEVEN SEGMENT DISPLAY DECODER/DRIVER

### SEVEN SEGENT DISPLAY UNIT

The display type used in this design is the light emitting diode (LED) seven-segment display. The LED was used because of its brightness, low cost, reliability and compatibility with low voltage integrated circuiting It can display the digit 0-9

Each decimal digit can be formed by lighting some subset of the seven segments as shown in figure.

# 2.7 BCD – TO 7 SEGMENT DECODER/DRIVER

A decoder is a circuit used to change a coded input such as BCD to another code. The CD4511b used in this design takes a 4-bit BCD input from the output of CD4029B counters and provide the outputs that passes current through the appropriate segments to display the decimal digit.

The LED used in this design is a common – cathode type where the cathodes of the segments are tied together is driven by a BCD to seven segment decoder/driver with active High outputs that apply a high voltage to the anodes of those segments to be activated. The seven-segment display is available in the form of an IC.

The anodes are connected to the output of the CD45511B decoder. All the anodes of the LEDs are connected through the current Limiting resistor, to the appropriate output of the decoder/driver. By controlling current through each LED, some segments will Light (1) and others will the dark (o) so that desired character pattern will be generated

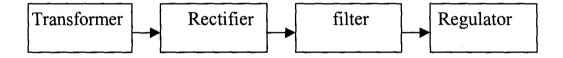

#### 2.8 POWER SUPPLY UNIT

Digital sound detector requires about 5V direct current for its operation. This is because of the readily availability of alternating current (AC) the latter was designed for this device. However in the absence of a.c or of so desired the device can be powered By the d.c

In the application of A.C, the voltage is to step to about 9 V by a transformer. The transformer also provides electrical isolations between the mains and the device. The rectifying circuit captures the new A.C voltage and convert at to D:C pulsating voltage. A regulation removes the pulse and delivers a constant voltage.

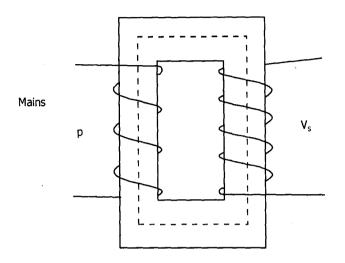

#### THE TRANSFORMER

A transformer is a device consisting of two closely coupled coils called primary and secondary. An a.c voltage applied to the primary

(Vp), appears across the secondary (Vs) with a voltage multiplication proportional to the turn ration of the transformer and current multiplication inversely proportional to thee turn .The voltage transformation ration (k) tell

whether it is step-down or step up. This, diodes of primary rating greater than 12v and with a forward current of 1 $\Lambda$  were chosen for the rectification.

For the filter capacitor, the ripple voltage of the rectifier output was estimated to be about 5V

Let v= ripple voltage

$$V = 5v$$

Let $\triangle$ t = time between peaks of the rectified input ware form.

$$\triangle t = \frac{1}{2}, F = \text{frequency of the mains} = 50H_2$$

$$= \frac{1}{2} = 10\text{ms}$$

$$= \frac{1}{2} \times 50$$

Recalled that,

$$I = C \triangle v$$

$$\triangle t$$

Let I = 1A (chosen)

$$C = I \triangle t = 1 \times 10 \text{ms}$$

$$\triangle v = 5$$

$$C = 2mF = 2000 UF$$

By reason of the above value, a capacitor 2200UF was used. Leaving room for allowance, the voltage rating of the filter capacitor was chosen to be twice the peak; hence a filter capacitor of 2200 vF and 25V was used.

Shown below is the complete air unit of the power unit.

## Power Supply Unit.

Fig. The transformer

K = an ideal transformer,

$$\frac{1}{K} = \frac{Vp}{Vs} = \frac{Is}{Ip}$$

If K > 1, the transformer is called step-up transformer

If  $K \le 1$ , then the transformer is called step-down transformer

K – voltage transformation ratio

Vp - voltage applied at the primary coil

$Vs-voltage \ delivered \ at the secondary \ coil.$

Np - No. of turns in primary

Ns – No. of turns in secondary

Ip – current applied at the primary coil

Is – current delivered at the secondary coil

A step down transformer of 12V was employed because 5V was needed to power the device.

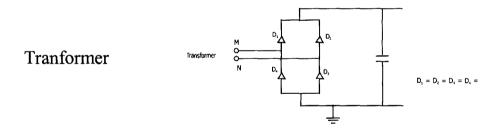

#### THE RECTIFIER

Rectification is the process where by an ac voltage is converted to d.c voltage. The circuit connection that does this is called a Rectifier. This is one of the simplest and most important applications of diodes.

Full-wave bridge rectifier was used in this project because of the following reason: the average current through a diode in full wave rectifier equals only half the d.c load current because there are too diodes in the circuit, each sharing the load. It has less ripple and produces twice as much as the output voltage of the three (half wave rectifier and full wave rectifier).

$$D_1 = D_2 = D_3 = D_4 =$$

During the positive input half -cycles terminal M of the secondary is positive and N is negative. Diodes Di and D3 become forward-biased (ON) where as D2 and D4 are reverse -biased (OFF). Hence, current flows round the load.

During the negative input half -cycle, secondary terminal N becomes positive and M negative. Now, D2 and D4 are forward biased. Circuit current flows round the whole circuit. Hence current keeps flowing during both half -cycles of the ac input supply.

The average dc voltage of the output voltage is given as

$$Vdc = 2Vp = 2\sqrt{2} Vs$$

where Vp and Vs are the peak and r.m.s value of the rectifier input voltage.

#### THE FILTERING CIRCUIT

The output voltage of the rectifier consists of ripples, which is not good for the operation of electronic appliance. To remove these ripples, a capacitor is used.

The capacitor charges up during the diode conduction period to the peak value and when the rectifier voltage falls below this, the capacitor discharges through the load. The filter capacitor is chosen large enough to provide acceptably low ripple voltage. This happens to be polarized electrolytic capacitor because its provides high values of capacitance in small package.

### THE REGULATOR

The output of the filter capacitor is a function of the input voltage. If supply directly to the circuit, this could damage the components. In order to keep the supply voltage constraint, a regulator is introduced. The regulator used is a positive 5V regulator because all the Ics employed in the circuit can be powered by five volt (5V). a capacitor is connected across the output terminal of the regulator in order to improve the transient response.

#### **SAFETY DEVICE**

A fuse of calculated value was employed to prevent excess current from flowing into the circuits.

## DESIGN SEQUENCE OF THE POWER SUPPLY UNIT

Most of the Ics used in this project are powered by five (v) supply and draws current in the range of micro and milli-Amp (vA and mA). Therefore, a 5V power supply that can deliver 1A is designed for it.

A transformer voltage of 9V was used

$$Vpeak = Vpeak = vrms \sqrt{2}$$

$$Vp = 12V$$

$$Vrms = \frac{Vp}{\sqrt{2}} = \frac{12}{\sqrt{2}}V$$

$$Vpeak = Vr.m.s \sqrt{2}$$

$$= 12\sqrt{2}$$

$$Vpeak = 17.00$$

With this value, the 12V transformer is suitable for the project. Protecting the circuit against current surges, a fuse is necessary and this is installed on the primary side of the transformer. For ideal transformer.

Power input = power output

$$P = Iv$$

$$:. I pVp = Is Vs$$

from above, up (rms) = 220 V, Vs (rms) = 9.0V, Is = 1A (chosen)

$$Ip = \frac{Is \ Vs}{Vp} = \frac{1x \ 9.0}{220}$$

Ip

$$\approx 41 \text{ m A}$$

Thus, at full load, a current of 41mA flows in the primary coil of the transformer. However, considering the healing effect of the primary current, current surges, filtering action of the capacitor and allowance for the fuse at full load.

Fuse rating =  $41 \text{mA} \times 6$  (allowance for current surges) x 2 (heating effect) x 2 (allowance for under excess load)

$$=$$

41 mA x 6 x 2 x

$$=$$

0.  $984A = 1A$

= 1A.

Therefore, a slow-blow fuse of current rating 1A was connected at the primary side of the transformer.

To calculate for the peak inverse voltage (PIV) of the diodes of the bridge rectifiers.

$$Vpeak = 12V$$

$$V dc = \frac{2Vpeak}{\Pi}$$

- for a full wave rectifier

$$Vdc = 2 \times 12V = 7.64 V$$

$$Vdc = 8V$$

#### **CHAPTER THREE**

### CONSTRUCTION, TESTING AND RESULTS

#### 3.1 CONSTRUCTION

The circuit was first connected on a breadboard. This go a long way in replaying of the component that may go bad in the course of testing. After displaying the output, the breadboard circuit was dismantle.

The final circuit was constructed on Vero-board. The power supply unit was constructed first with the power supply indicator. This helps in determining the certainty of the flow of power into the circuit. The components were positioned on the board by poking their leads through the holes from the side opposite to the copper tracks. All components were placed before soldering, this is permit better judgement and connection linkage between the components.

PVC covered 0.6mm diameter wire was used for the wire links. To make a good soldered joint, the tip of the soldering iron was in contact with both the copper tract and the wire to be soldered to the track. It was ensured that the solder flows off the tip of the soldering iron and around the wire to be soldering without going as far as the two adjacent holes. This operation takes no more than about fries (5) seconds otherwise the heat conducted through the wire night damage the components. To prevent the integrated circuits (IC) from been damaged as a result of heat from the soldering iron, each of them were inserted into socket called IC socket.

After all the component and wire links have been soldered in place and all the joints checked over with magnifying glass: the errors detected were corrected.

Another problem observed was that of the short circuit. This was detected with the help of the multimeter's continuity alarm test provision. The alarm helps a lot and it is hereby recommended. Two IC pins lying on the same conducting path were etched to disconnect them from each other. As a result of unavailability of etching solution, etching was done using razor blade.

#### **PROJECT CASING**

The entire circuit was housed in wood casing. A wood casing was preferred to other (such as plastic, metal) for reason of lightness and durability.

The appropriate holes and cuts were made as shown for the power cable, switch, and fuse. Slits were made at the side to allow air flows –ventilation.

#### CONTRUCTION TOOLS USED

Some of the construction tools used during the hardware construction are listed below:

(i) Bread board and insulated copper wire: these were used to house and connect other component in building a prototype model for test and design modification.

- (ii) Vero board: this was where the working circuit was finally mounted and solder permanently.

- (iii) Soldering iron and Lead: A 40W soldering iron and lead were used in soldering the entire component on board.

- (iv) Wire cutter, blade and pliers: These were used in cutting wires to appropriate length and cutting the legs of components to prevent short circuit.

- (v) Suction tube: This was used to suck desoldered lead away from unwanted area. This tool really helps.

- (vi) Digital Multimeter: This device was used to test continuity of lines and to measure voltages, currents and resistance output of the component in the circuit during construction.

## 3.2 TESTING AND RESULTS

Each component was tested at every stage and the results noted. Since the power supply unit supplies power to all the components, its efficiency is highly important.

When the power from the mains was delivered to the power supply unit, the power indicator was lighted. A multimeter was used to measure the voltage at the output of the rectifier, regulator, power pins of each I.C., the ground of each I.C., the input and output of each I.C.

| S/NO | TIME (mints) Turning freq. (HZ) | DIGITAL SOUND (freq. HZ) |

|------|---------------------------------|--------------------------|

| 1.   | 256                             | 256                      |

| 2.   | 480                             | 480                      |

| 3.   | 271.2                           | 271.2                    |

| 4.   | 288                             | 288                      |

## 3.3 PROBLEMS ENCOUNTERED

In the course of this project, some problems were encountered. Theses include.

- (i) Unavailability of components as specified in the original design, led to the use of closer alternative and in some cases redesigning of some of the units in the circuit diagram.

- (ii) Erratic power supply slowed down the pace of the project.

- (iii) Due to time constraints, some good features that would have further enhanced the project could not be added.

#### **CHAPTER FOUR**

# DISCUSSION, CONCLUSION AND RECOMMENDATION

#### 4.1 DISCUSSION OF RESULT

The Digital Sound Detector has been designed and constructed based on the knowledge of circuit theory, electronics and computer engineering courses.

After all the required connections were made, it powered and the result was satisfactory. This proves the success of the device.

## 4.2 **CONCLUSION**

In conclusion, the aims/objectives of the work has been achieved. Sound frequency can be detected and displayed on seven segment display.

#### 4.3 **RECOMMENDATION**

The result obtained from this project would have been more satisfactory if not for high cost and scarcity of components. This project can be improved or advanced with the availability of resources and components.

## REFERENCE

- 1. Analog Devices, 2002 WWW Analog. Com

- 2. Hertz Heinrich Rudolf (1857) Frequency of Radio Wave.

- 3. JWS Rayleigh (1945) "Theory of sound".

- 4. National Semi Conductor, 2002 WWW National. Com.

- 5. Ronald J.T Neal S.W (1998), Digital Systems, Principles and Applications" 7<sup>th</sup> Edition, Prentice Hall, U.K